# SERIES II CNC MILLING, DRILLING AND BORING MACHINE (BOSS 6 AND 6.2 CONTROLS) MAINTENANCE MANUAL

志

February 1982

Missing Sheets 2-1, 13-19, 13-20 I would VERY MUCH Like to thank John Lafergola for compiling this book from individual Pictures.

Bridgeport Machines Division of Textron Inc.

ATP REV.0

Code No. 11040307

# TABLE OF CONTENTS

| Section | Page                                     | 3 |

|---------|------------------------------------------|---|

| 1       | INTRODUCTION                             |   |

|         | 1.1 Purpose 1.1                          |   |

|         | 1.2 Scope 1-1                            |   |

|         | 1.3 Referenced Manuals1-1                |   |

|         | 1.4 Specifications 1-1                   |   |

| 2       | THEORY OF OPERATION                      |   |

| -       | 2.1 Introduction                         |   |

|         | 2.2 System Architecture                  |   |

|         | 2.3 LSI-11 Processor                     |   |

|         | 2.4 LSI-Bus                              |   |

| 3       | POWER DISTRIBUTION                       |   |

|         | 3.1 Power                                |   |

|         | 3.2 Regulated Power Supply Adjustment3-1 |   |

| 4       | LOGIC BOARDS                             |   |

|         | 4.1 Introduction                         |   |

|         | 4.2 Universal Front Panel Logic Board4-1 |   |

|         | 4.3 ZDI Logic Board                      |   |

|         | 4.4 ZCK Logic Board                      |   |

|         | 4.5 NTP Logic Board                      |   |

|         | 4.6 ERS Logic Board                      |   |

|         | 4.7 RRS Board                            |   |

|         | 4.8 SCA Board                            |   |

|         | 4.9 Logic Board Schematics               |   |

| 5       | AXIS DRIVE SYSTEM                        |   |

|         | 5.1 Introduction                         |   |

|         | 5.2 SMD Board                            |   |

|         | 5.3 Power Drivers                        |   |

|         | 5.4 Axis Drive Signals                   |   |

|         | 5.5 ACC Board and Saturable Reactors5-2  |   |

|         | 5.6 Adjustment of ACC Board5-2           |   |

| 6       | TROUBLESHOOTING                          |   |

|         | 6.1 Introduction                         |   |

|         | 6.2 Logic Board Cleaning                 |   |

|         | 6.3 Electrical Tests                     |   |

|         | 6.4 Jog Mode Tests                       |   |

| 7       | TESTS                                    |   |

|         | 7.1 Introduction                         |   |

|         | 7.2 ZCK Board Test and Adjustment7-1     |   |

|         | 7.3 Diagnostic Tapes7-3                  |   |

|         | 7.4 Interrupt Test                       |   |

|         | 7.5 ODT (Octal Debugging Technique)7-9   |   |

| 8       | MACHINE COMPONENTS                       |   |

|         | 8.1 Overview                             |   |

|         | 8.2 X and Y Axes                         |   |

|         | 8.3 Z-Axis Drive                         |   |

|         | 8.4 Milling, Drilling and Boring Head    |   |

|         | 8.5 Knee Drive8-5                        |   |

Bridgebort, TEXTRON

| Section |                                                                                       | Page                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 8.6<br>8.7<br>8.8                                                                     | Lubrication System                                                                                                                                                                                                                                                                                                                                                                                    |

| 9       | <b>PREVE</b><br>9.1<br>9.2<br>9.3                                                     | Introduction       9-1         Lubricating System       9-1         Routine Maintenance       9-1                                                                                                                                                                                                                                                                                                     |

| 10      | BASE<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7                          | ASSEMBLY10-1Introduction10-1X and Y-Axis Counters10-1X and Y-Axis Drive Motors10-5X and Y-Axis Ballscrews10-7Limit Switches10-10Table and Saddle10-12Manually Operated Knee Drive10-12                                                                                                                                                                                                                |

| 11      | HEAD<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10 | ASSEMBLY. 11-1<br>Introduction 11-1<br>Lubrication 11-1<br>Head Removal 11-1<br>Power Transmission 11-1<br>Quill and Spindle 11-4<br>Quill Limit Switches 11-6<br>Alignment of Quill Housing to Drive Motor<br>Housing 11-10<br>Ball Quill Extension Inspection 11-10<br>Removal of Manual Speed Changer and Brake<br>Lock Mark II. 11-10<br>Pneumatic Speed Changer and Brake Lock<br>Mark II. 11-12 |

| 12      | OPTION<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7                        | NAL EQUIPMENT12-1Introduction12-1Installation of Y-Axis Reed Clamp12-1Y-Axis Disconnect Cable Installation12-1Cushman 12" Rotary Table and Drive12-3Hofmann Rotary Table12-5Option I4: Indexing12-7Option K: Coolant System12-8                                                                                                                                                                       |

|         | PARTS<br>13.0<br>13.1<br>13.2<br>13.3<br>13.4<br>13.5                                 | LIST — CONTROL                                                                                                                                                                                                                                                                                                                                                                                        |

| 14      | масні                                                                                 | NE — PARTS LISTS       14-1         Machine Assemblies Index       14-1         Options       14-14         Recommended Mechanical Spares       14-18                                                                                                                                                                                                                                                 |

#### Bridgebort TEXTRON

# LIST OF ILLUSTRATIONS

| Figure       |                                                    | Page  |

|--------------|----------------------------------------------------|-------|

| 2-1          | CNC BOSS 6 Simplified Block Diagram                | . 2-1 |

| 2-2          | Simplified Computer Structure                      | .2-2  |

| 2-3          | Map of BOSS 6                                      | 2-3   |

| 2-4          | LSI-11 Pin Assignments                             | 2-4   |

| 2-5          | DATI Bus Cycle                                     |       |

| 2-6          | DATIO or DATIOB Bus Cycle                          | 2.9   |

| 2-7          | DATO or DATOB Bus Cycle                            | 2.10  |

| 2-8          | Interrupt Request/Acknowledge Sequence             | 2.11  |

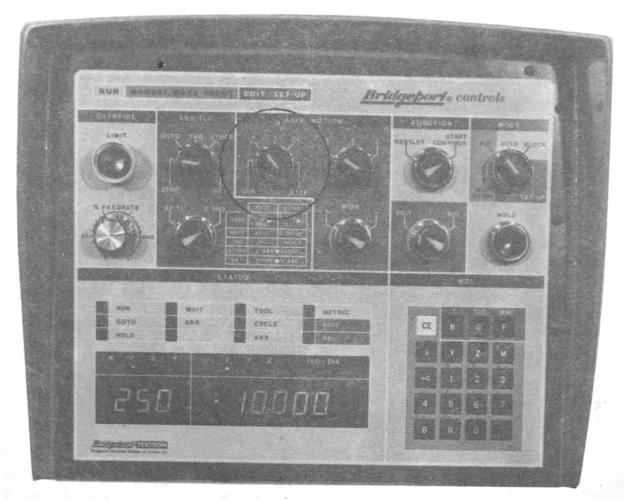

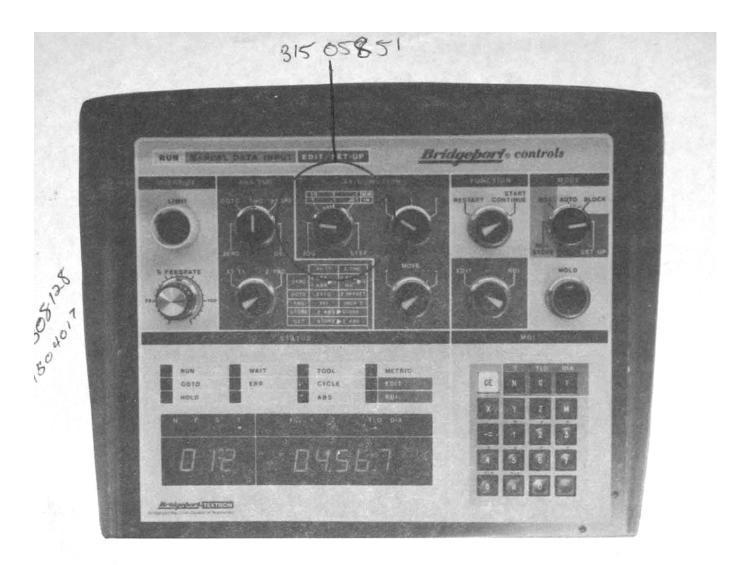

| 4-1          | Operator's Main Control Panel S/N 7000 to S/N 7409 |       |

| 4-2          | Operator's Main Control Panel S/N 7410 and After   |       |

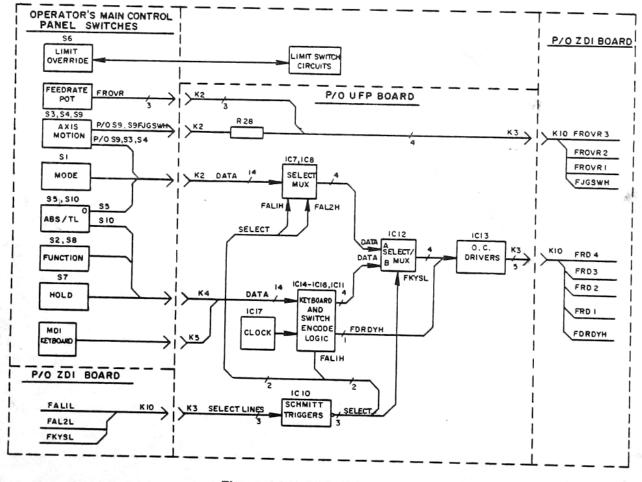

| 4-3          | UFP Switch Interface                               |       |

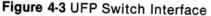

| 4-4          | UFP Display Interface.                             | 4-3   |

| 4-5          | External Switch Interface Simplified Block Diagram | 4-4   |

| 4-6          | ZDI Interrupt Circuits                             | 4-11  |

| 4-0          | ZDI Interrupt Circuits Simplified Block Diserver   | 4-12  |

| 4-7<br>4-8   | ZDI Interrupt Circuits Simplified Block Diagram    |       |

| 4-8<br>4-9   | ZDI Tape Reader Interface                          |       |

|              | Spindle Off and X-Axis SMD                         |       |

| 4-10         | NTP Block Diagram                                  | 4-18  |

| 4-11         | Interpolation Algorithm                            | 4-21  |

| 4-12         | Linear Interpolation Algorithm                     | 4-22  |

| 4-13         | Circular Interpolation Algorithm                   | 4-23  |

| 4-14         | Block Diagram of Serial Interface                  | 4-26  |

| 4-15         | Local Serial Interface                             |       |

| 5-1          | Axis Drive Waveforms (Sheet 1)                     | 5-3   |

|              | Axis Drive Waveforms (Sheet 2)                     | 5-4   |

|              | Axis Drive Waveforms (Sheet 3)                     | 5-5   |

|              | Axis Drive Waveforms (Sheet 4)                     | 5-6   |

| 5-2          | Sigma and Superior Windings                        | 5-7   |

| 6-1          | Sequence of Electrical Checks                      | 6-2   |

| 6-2          | Electrical Power Test                              | 6-3   |

| 6-3          | Power Equipment Enclosure                          | 6-5   |

| 6-4          | Control Equipment Enclosure                        | 6-6   |

| 6-5          | Regulated Power Supply                             | 6-7   |

| 6-6          | Fuse Chart                                         | 6-8   |

| 6-7          | Electrical Function Test                           | 6-9   |

| 7-1          | Diagnostic Tape Test Flow Chart                    | 7-5   |

| 7-2          | ZDI/Front Panel — Sample Printout                  | 7-6   |

| 7-3          | Sample of Responses to ZDI Test                    | 7-6   |

| 7-4          | Sample Memory Text Printout                        | 7-7   |

| 7-5          | Sample Printout of Processor Test                  | 7.7   |

| 7-6          | Sample Printout of Traps Test                      | 7-8   |

| 7-7          | PROM Test Error Printout Sample                    | 7.9   |

| 8-1          | Step Motor                                         | 2.1   |

| 8-2          | X-Axis and Y-Axis Drive Transmission               | 3.2   |

| 8-3          | Knee Drive Transmission                            | 2.2   |

| 8-4          | Z-Axis Limit Switches                              | 2.2   |

| 8-5          | Spindle Drive Transmission                         | 22    |

| 8-6          | Milling, Drilling and Boring Head                  | 2.4   |

| 8-7          | Column Knee Clamps                                 | 25    |

| 8-8          | Automatic Lubricator                               |       |

| 8-9          | Gib Locations                                      | 5-5   |

| 8-10         | Knee Guiding Gib Adjustment                        | 0.0   |

| 8-11         | Knee to Column Gib Adjustment                      | -9    |

| 8-12         | Y-Axis Gib Setting                                 | 9-9   |

| 8-12         | Y-Axis Gib Setting                                 | 5-10  |

| 8-14         | X-Axis Gib Setting                                 | 5-10  |

| 0-14<br>10-1 | Pneumatic System                                   | 5-11  |

| 10-1         | X-Axis Drive and Counter Assembly1                 | 0-2   |

|              | Timing Belt Tensioning                             | 0-3   |

| 10-3         | Y-Axis Drive and Counter Assembly                  | 0-4   |

| 10-4         | Tape Lock Bushing Installation1                    | 0-6   |

Bridgeport, TEXTRON

| Figure |                                                    | Page  |

|--------|----------------------------------------------------|-------|

| 10-5   | Field Alignment of Z-Axis Ballscrew                | 10-9  |

| 10-6   | X-Axis Limit Switch Assembly                       | 10-11 |

| 10-7   | Y-Axis Limit Switch Installation                   |       |

| 10-8   | Table Removal and Installation                     |       |

| 10-9   | Saddle Installation                                |       |

| 10-10  | Knee Elevating Crank Assembly                      |       |

| 10-11  | Z-Axis Pedestal and Cylinder                       |       |

| 10-12  | Removal of Knee                                    | 10-17 |

| 11-1   | Special Tool ST-6921 Head Lift Bracket             |       |

| 11-2   | Quick Change Locknut Assembly                      |       |

| 11-3   | Quill Limit Switch Assembly                        |       |

| 11-4   | Ball Quill Extension Torque on Nut Setup           |       |

| 11-5   | Ball Quill Extension Flushing                      |       |

| 11-6   | Ball Quill and Nut Flushing.                       |       |

| 11-7   | Removal of Brake Lock Mark II                      |       |

| 11-8   | Pneumatic Speed Changer - Mark II                  |       |

| 11-9   | Pneumatic Brake                                    |       |

| 12-1   | Y-Axis Reed Clamp Installation                     |       |

| 12-2   | Hole Locations for Y-Axis Disconnect Cable Bracket |       |

| 12-3   | Y-Axis Disconnect Cable for Rotary Table           | 12-3  |

| 12-4   | Cushman 12" Rotary Table                           | 12-4  |

| 12-5   | Hofmann 10" Rotary Table                           | 12-6  |

| 12-6   | Indexer Timing Sequence and Wiring                 | 12-9  |

| 13-1   | Operator's Control Panel Rear View                 | 13-1  |

| 13-2   | Control Equipment Enclosure                        |       |

| 13-3   | Control Equipment Enclosure (Detail)               |       |

| 13-4   | Regulated Power Supply Diodes                      | 13-5  |

| 13-5   | Regulated Power Supply Inside View                 | 13-6  |

| 13-6   | Regulated Power Supply Heat Sink and Transistor    |       |

|        | Assembly                                           |       |

| 13-7   | Axis Drive Chasis                                  |       |

| 13-8   | Axis Power Drive Heat Sink Assembly                |       |

| 13-9   | Power Equipment Enclosure                          |       |

| 13-10  | Starter Brake Spindle Speed Housing                |       |

| 13-11  | Pneumatic Diagram                                  |       |

| 13-12  | Pneumatic Installation, Index Option               |       |

| 13-13  | Pneumatic Assembly Detail                          |       |

| 13-14  | Pneumatic Assembly Detail                          |       |

| 13-15  | ERS Board.                                         |       |

| 13-16  | ZCK Board                                          |       |

| 13-17  | NTP Board                                          |       |

| 13-18  | ZDI Board                                          | 13-21 |

Ż

# LIST OF TABLES

| ⊢igure |                                           | Page |

|--------|-------------------------------------------|------|

| 2-1    | LSI-11 Pin Assignments                    | 2-5  |

| 4-1    | IC7 and IC8 Data Selection                | 4-5  |

| 4-2    | Encoder and PROM Output                   | 4-6  |

| 4-3    | UFP Switch Multiplex Selection            | 4-7  |

| 4-4    | Address Decoding Logic of Drawing 1040274 | 4-9  |

| 4-5    | NTP Registers                             |      |

| 5-1    | Axis Drive Signal Sequence                | 5-1  |

| 12-1   | Ordering Data                             | 12-8 |

|        |                                           |      |

# SECTION I

£#0736 -<

# X Travel

#### 1.1 PURPOSE

In this manual we provide the information necessary to maintain the Bridgeport Series II CNC Milling, Drilling and Boring machine with Bridgeport Operating System Software (BOSS) Level 6.0. Our intention is to provide the resources for diagnosing mechanical or computer problems as well as to provide the means to solve them.

We also address the prevention of problems with a checklist of preventive maintenance procedures. Be sure to read and follow all preventive maintenance procedures shown in Section 9.

This manual is geared to meet the needs of three levels of maintenance, defined as follows:

Level 1 (Operator) The machine operator (or other customer representative) is not assumed to have any detailed knowledge of the equipment. The operator is not assumed to use electrical tools for maintenance.

Level 1 maintenance consists of keeping the equipment clean, lubricating and ensuring that lubricant reservoirs are full, making sure that power is turned on, and following proper startup and operating procedures.

Level 1 personnel are not authorized to make adjustments or replace components.

Level 2 (Dealer Service or specially trained customer personnel) Level 2 service personnel are assumed to have a fair knowledge of the equipment. They are assumed to have VOMs, spare fuses, printed circuit boards and diagnostic tapes.

Level 2 maintenance consists, in addition to all Level 1 procedures, of adjustment of power supply voltages and replacement of major subassemblies, such as step motors, cables, PC boards, fuses, etc., plus certain individual components such as contactors, power switches and disconnects.

Level 2 personnel are not authorized to adjust clock rates or to replace individual components other than those enumerated above.

Level 3 (BMI Field Service or other specially trained personnel) Level 3 maintenance personnel are trained at Bridgeport service school. They are expected to have a detailed knowledge of the equipment and theory of operation.

Level 3 maintenance personnel are equipped with all the tools available to Level 2 personnel plus oscilloscopes and logic probes.

Level 3 maintenance personnel are authorized to perform, in addition to all Level 2 maintenance functions,

adjustment of clock rates and replacement of certain individual components such as power semiconductors, filter capacitors, and integrated circuits.

#### 1.2 SCOPE

Sections 1 through 14 of this manual consist of two main parts: Control and Machine.

Sections concerning the Control, provide a theory of operation of the control system, the power distribution, description of the PC boards, the axis drive system, troubleshooting procedures and tests. Maintenance procedures are Level 2 and 3.

The Machine sections concerning the theory of operation, contain preventive maintenance and information on mechanical maintenance and parts replacement. Most of these procedures are Level 1 and 2.

The Appendix contains parts lists. The Machine lists are organized by assembly; the Control lists are organized by function, e.g. electro-mechanical parts, resistors, cables, etc. The Appendix also contains the wiring diagrams, block diagrams and schematics specially segmented for clarity.

#### **1.3 REFERENCED MANUALS**

The following manuals for this machine are referenced:

M-142 Installation Manual M-140 Operating Manual

M-139 Programming Manual

#### 1.4 SPECIFICATIONS

| RANGE                  | INCH      | METRIC  |

|------------------------|-----------|---------|

| Table Travel (X Axis)  | 30″       | (760mm) |

| Saddle Travel (Y Axis) | 15 ″      | (380mm) |

| Quill Travel (Z Axis)  | 5″        | (127mm) |

| Knee Travel (Manual)   | 13-3/16″  | (337mm) |

| Throat Distance        | 15-9/16″  | (395mm) |

| Table to Spindle       | 7″        | (177mm) |

| Gage Line Minimum      |           |         |

| Maximum Vertical       | 1000 Lbs. | (454kg) |

| Load Uniform           |           |         |

| Distribution           |           |         |

|                        |           |         |

#### TABLE

| Overall Size    | 47x16-5/8″  | (1195x425mm)    |

|-----------------|-------------|-----------------|

| Working Surface | 38x15″      | (960x380mm)     |

| T-Slots         | 3 on 4-3/8″ | (3 on 111.125mm |

|                 | Centers     | centers)        |

| T-Slot Size     | 5/8″        | (15mm)          |

| Position Speed  | 100 ipm° /  | (2540mm/min)    |

| Height Above    | 50″         | (1270mm)        |

| Floor-Maximum   | ** **       | 14. °           |

|                 |             | 6               |

#### Bridgebort TEXTRON

| SPINDLE                               |                  |                   | CONTROL OVATEM                 |                        |                                       |

|---------------------------------------|------------------|-------------------|--------------------------------|------------------------|---------------------------------------|

| Motor Rating                          | 2 HP             | (1.5kw)           | CONTROL SYSTEM                 | 2081//2201//           | COV /and tatal                        |

| Power Rating                          | 1-1.75 HP        | (.75-1.4kw)       | Control Power                  |                        | 60V (see total                        |

| Taper                                 | #30 Quick        | or #200 Universal | Supply-                        | power below            | N)                                    |

| , ap et                               | Change           | (optional)        | 60 Hz, 3 Phase                 | 10.10                  |                                       |

| Speed Range                           | 60-4200          | (optional)        | Control Power                  | 12a/6a per p           | onase                                 |

|                                       | RPM              |                   | Power Requirements<br>(3-Axis) | 2.7 KVA                |                                       |

| Transmission Ratios                   | 1:1 and<br>8.3:1 |                   | System                         |                        | ental CNC, Rec-<br>Polar Coordinate I |

| Rapid Approach Rate                   | 100 ipm          | (3048mm/min)      |                                | put                    |                                       |

| (Z Axis)                              |                  |                   | Format                         |                        | ss Variable Block                     |

| Controlled Downfeed<br>Range (Z Axis) | .2-51.0 ipm      | (5-1295mm/min)    | Format Detail                  |                        | ' + 34Z + 34R34A +                    |

| Drilling Capacity-                    | 3/4 "            | (19mm dia.)       | Reference EIA                  | RS-227,RS-2            |                                       |

| Mild Steel                            | Diameter         | (                 | Standards                      | h3-227,h3-2            | 740,83-336                            |

| Milling Capacity-                     | 1.5 cu.          | (25cc/min)        | Standards                      |                        |                                       |

| Mild Steel                            | Ins/min          | (2000///////      | CNC FEATURES                   |                        |                                       |

| Boring Range                          | To 4"            | (To 102mm dia.)   | Storage Capacity               | 90 ft of ogui          | valent EIA RS-358                     |

|                                       | Diameter         | (                 | Storage Capacity               | •                      | valent EIA HS-356                     |

| Tapping Range                         | #5-40 TO         |                   | Subroutines                    | tape<br>36 Macros      |                                       |

| W/tapping                             | 1/2-13           |                   | Repetitive                     |                        | noted lanes                           |

| attachment                            |                  |                   | Programming                    | 4 Levels Of I          | nested loops                          |

| Spindle Diameter                      | 1-3/8 "          | (35mm)            | Transformation                 | Rotation or S          | Cooling                               |

| Quill Diameter                        | 3-3/8 "          | (86mm)            | Editing                        | 20 Command             |                                       |

|                                       |                  |                   | Part Program                   |                        |                                       |

| MILLING                               |                  |                   | Loading                        |                        | (optional) or                         |

| Feedrate                              | .2-51.0 ipm      | (2-1295mm/min)    | Data Input Device              | Data Input D           |                                       |

| Feed Increments                       | .1 ipm           | (1mm/min)         | Data input Device              |                        | nterface @ 20 ma                      |

| Override-                             | 1-120%           |                   | Maintenance                    | or RS-232              |                                       |

| Infinitely Variable                   | Constant To      | (1295mm/min)      | Maintenance                    | Diagnostic F           | loutines                              |

| Vector Feedrate                       | 51 ipm           | (,                | SPACE AND WEIGHT               |                        |                                       |

| Control (XYZ)                         |                  |                   | Floor Area                     | 90 // V 70 //          | (0000)(1770                           |

|                                       |                  |                   | Height                         | 80″ X 70″              | (2032X1778mm)                         |

| POSITIONING                           |                  |                   | Weight (W/control)             | 89″                    | (2260mm)                              |

| Rapid Traverse XYZ                    | 100 ipm          | (2540mm/min)      | Shipping Weight                | 5000 lbs.<br>5400 lbs. | (2272kg)<br>(2455kg)                  |

| MACHINE AND CONT                      | ROL PERFOR       | MANCE             | POWER                          |                        |                                       |

| Positioning Accuracy                  | +/001"           |                   | Electrical Supply-             | 222242224              |                                       |

|                                       | in center        |                   | 60 Hz, 3 Phase                 | 230V/460V SI           | ngle Connection                       |

|                                       | 24″              |                   |                                | or 208V on S           |                                       |

| Positioning                           | +/0005″          | (0.013mm)         | Main Power Breaker             | 20A/10A per            | phase                                 |

| Repeatability                         |                  |                   | Electrical Rating              | 5KVA                   |                                       |

| Output Resolution                     | .0005″           | (0.013mm)         | COLOR                          |                        |                                       |

| Input Resolution                      | .0001″           | (0.001mm)         |                                |                        |                                       |

| Jog Increments                        | 1″,.1″, .01″,    | (After serial     | Standard                       | Machine Too            | Gray                                  |

|                                       | .0005″           | #9100,            |                                |                        |                                       |

|                                       |                  | 10mm, 1mm,        |                                |                        |                                       |

|                                       |                  | .1mm, .0005mm)    |                                |                        |                                       |

|                                       |                  | ,                 |                                |                        |                                       |

Incremental CNC, Recular or Polar Coordinate Ind Address Variable Block 2X + 34Y + 34Z + 34R34A + 4j34k34f21S4t2m2 227,RS-274C,RS-358

.

#### 2.3 LSI-11 PROCESSOR

#### 2.3.1 Operation

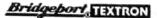

Figure 2-2 shows a simplified computer structure. In general, the processor consists of various functional parts:

- A programmable arithmetic/logic unit (ALU) that can act as many of the logic elements used in a random logic system. For example, it can add, subtract, increment, decrement, AND, OR, and compare the result of an operation to zero.

- Processor control logic that analyzes the various programmed instructions and causes the system to generate a sequence of events which will execute the instruction.

- Bus Input/Output control that enables communication to and from the processor.

Two types of information are passed through the bus: the address and the data. The address is the physical location of the data to be used.

#### 2.3.2 Addressing Memory

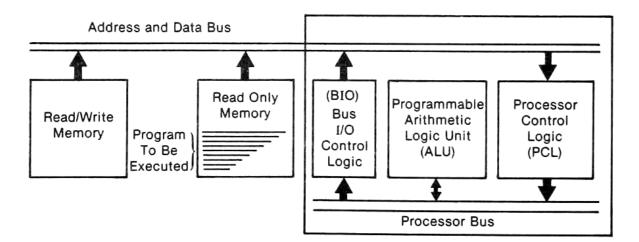

Figure 2-3 shows a memory map of the Series II CNC system. Note that the LSI-11 uses a 16 bit word. This means that 65,536 unique locations can be directly addressed. However, the LSI-11 directly addresses both bytes (8 bits) and words (16 bits). An LSI-11 word consists of a high byte and a low byte.

Word addresses are always even numbered. Byte addresses can be either even or odd numbered. Low bytes are stored at even numbered memory locations and high bytes at odd-numbered memory locations.

Considering the system as word organized, the LSI-11 can directly address 32K words.

NOTE

For convenience, values will be given in octal code. A 16-bit word would be represented as follows:

| -  |    |    |    |   |    | 10 | ١E | wo | RD | - |   |   |   |   | ~   |

|----|----|----|----|---|----|----|----|----|----|---|---|---|---|---|-----|

| 15 | 14 | 13 | 12 | П | 10 | 9  | 8  | 7  | 6  | 5 | 4 | 3 | 2 | 1 | 0   |

| 1  | 1  | 0  | 0  | 0 | 1  | 0  | 0  | .0 | 1  | 1 | 1 | 0 | 0 | 0 | . 1 |

| 1  | +  | 4  |    |   | 2  |    |    | 1  |    | - | 6 |   | 1 | 1 |     |

This is 142161 in octal.

The same data as 2 bytes would be:

| HIGH BYTE |     |    |    |      |    |    | -   |   | - L( | wc | 871 | Έ-  |   | -   |     |

|-----------|-----|----|----|------|----|----|-----|---|------|----|-----|-----|---|-----|-----|

| 15        | ,14 | 13 | 12 | , 11 | 10 | ,9 | , 8 | 7 | 6    | 5  | 4   | , 3 | 2 | , 1 | 0   |

| 1         | 1   | 0  | 0  | 0    | 1  | 0  | 0   | 0 | 1    | 1  | 1   | 0   | 0 | 0   | , ' |

|           | 3   |    | 0  |      |    | 4  |     |   | I    |    | 6   |     |   | 1   |     |

161 - Iow byte 304 - high byte

Figure 2-2 Simplified Computer Structure

Data can be of two kinds:

- 1. Data to be operated on by the system. For example, the value 2.

- Instructions to be executed by the system. For example, the instruction ADD, A, B, would be 066767.

#### 2.3.3 Program Levels

There are three hierarchical levels of program instructions in the Series II CNC system:

- The micro program. It tells the processor how to execute a particular instruction. The micro program can only be modified by DEC.

- The macro program. BOSS (Bridgeport Operating Software System) is a set of instructions that make the system perform as an NC. BOSS is contained in read only memory, and should only be modified by Bridgeport-Textron.

The part program. This is input by the user to cause the control to machine a work piece.

#### 2.4 LSI-BUS

#### 2.4.1 Lines

The LSI-11 Bus consists of 17 control lines and a 16 line data/address bus. Address/data and control lines are open collector lines which are asserted low.

#### 2.4.2 Pin Assignments-Figure 2-4

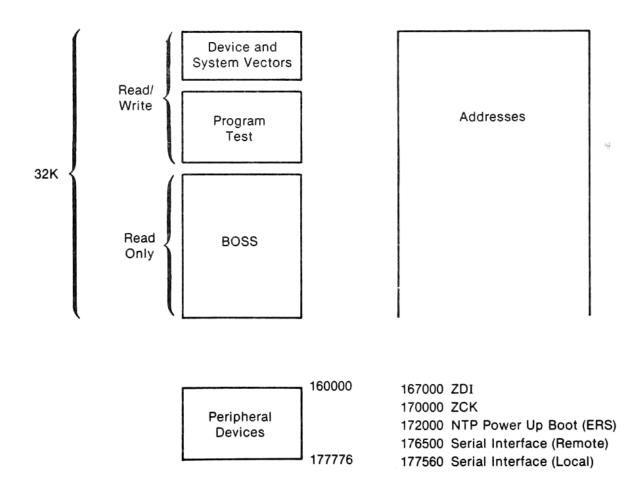

Table 2-1 shows the bus pin assignments. Each slot shown as ROW A and ROW B in Figure 2-4, includes a numeric identifier for the side of the module. The component side is designated side "1" and the solder side is designated side "2". Letters ranging from A through V (excluding G, I, O, Q) identify a particular pin on a side of a slot.

Figure 2-3 Map of BOSS 6

Bridgebort, TEXTRON

A typical pin is designated as: B E 2 SLOT (ROW) INDENTIFIER "SLOT B" PIN IDENTIFIER "PIN E" MODULE SIDE IDENTIFIER "SOLDER SIDE" All slot A pins are connected on the backplane to the corresponding slot C pins. All slot B pins are connected on the backplane to the corresponding slot D pins. Refer to Drawing 1040213.

Figure 2-4 LSI-11 Pin Assignments

Code No. 11040307 FEB 82 REV. 0 2-4

Bridgeport TEXTRON Bridgeport Machines Division of Textron Inc.

|            |                    | TABLE 2-1 LSI-11 PIN ASSIGNMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUS PIN    | MNEMONIC           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AA1        | BSPARE1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AB1        | BSPARE2            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AC1        | BSPARE3            | Bus Spares (Not assigned. Reserved for DIGITAL use).                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AD1        | BSPARE4            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AE1<br>AF1 | SSPARE1<br>SSPARE2 | Special Spares                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AH1        | SSPARE2<br>SSPARE3 | (Not connected to LSI-11.<br>Connected to other sockets.)                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AJ1        | GND                | Ground: System signal ground and DC return.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AK1        | MSPAREA            | Maintenance Spares                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AL1        | MSPAREA            | (Not connected to LSI-11. Connected to other sockets.)                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AM1        | GND                | Ground: System signal ground and DC return.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AN1        | BDMR L             | <b>Direct Memory Access (DMA) Request:</b> A device asserts this signal to re-<br>quest bus mastership. The processor arbitrates bus mastership between<br>itself and all DMA devices on the bus. If the processor is not bus master (it<br>has completed a bus cycle and BSYNC L is not being asserted by the pro-<br>cessor), it grants bus mastership to the requesting device by asserting<br>BDMGO L. The device responds by negating BDMR L and asserting BSACK<br>L. |

| AP1        | BHALT L            | <b>Process or Halt:</b> When BHALT L is asserted, the processor responds by halting normal program execution. External interrupts are ignored but memory refresh interrupts (enabled if W4 on the process module is removed) and DMA request/grant sequences are enabled. When in the halt state, the processor executes the ODT microcode and the console device operation is invoked.                                                                                     |

| AR1        | BREF L             | <b>Memory Refresh:</b> Asserted by processor microcode-generated refresh inter-<br>rupt sequence (when enabled) or by an external device. This signal forces<br>all dynamic MOS memory units to be activated for each BSYNC L/BDIN L<br>bus transaction.                                                                                                                                                                                                                    |

| AS1        | PSPARE3            | Spare (Not assigned. Customer usage not recommended).                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AT1        | GND                | Ground: System signal ground and DC return.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AU1        | PSPARE1            | Spare (Not assigned. Customer usage not recommended).                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AV1        | + 5B               | + 5V Battery Power: Secondary + 5V power connection. Battery power can be used with certain devices.                                                                                                                                                                                                                                                                                                                                                                        |

| BA1        | BDCOK H            | <b>DC Power OK:</b> Power supply-generated signal that is asserted when there is sufficient DC voltage available to sustain reliable system operation.                                                                                                                                                                                                                                                                                                                      |

| BB1        | врок н             | <b>Power OK:</b> Asserted by the power supply when primary power is normal.<br>When negated during processor operation, a power fail trap sequence is in-<br>itiated.                                                                                                                                                                                                                                                                                                       |

| BC1        | SSPARE4            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BD1<br>BE1 | SSPARE5<br>SSPARE6 | Not connected to LSI-11.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BF1        | SSPARE7            | Connected to other sockets.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BH1        | SSPARE8            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BJ1        | GND                | Ground: System signal ground and DC return.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BK1        | MSPAREB            | Not connected to LSI-11.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BL1        | MSPAREB            | Connected to other sockets.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BM1        | GND                | Ground: System signal ground and DC return.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BN1        | BSACK L            | This signal is asserted by a DMA device in response to the processor's BDMGO L signal, indicating that the DMA device is bus master.                                                                                                                                                                                                                                                                                                                                        |

| BP1        | BSPARE6            | Bus Spare (Not assigned, Reserved for DIGITAL use).                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BR1        | BEVNT L            | External Event Interrupt Request: When asserted, the processor responds (if PS bit 7 is 0) by entering a service routine via vector address 100. Used in I-CNC for feedrate clock pulse interrupt.                                                                                                                                                                                                                                                                          |

| BS1        | PSPARE4            | Spare (Not assigned. Customer usage not recommended).                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BT1        | GND                | Ground: System signal ground and DC return.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BU1        | PSPARE2            | Spare (Not assigned. Customer usage not recommended).                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Bridgebort, TEXTRON

| BV1        | +5                 | +5V Power: +5V DC system power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AA2        | +5                 | + 5V Power: Normal + 5V DC system power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AB2<br>AC2 | – 12<br>GND        | - 12V Power: - 12 DC optional power for devices requiring this voltage.<br>Ground: System signal ground and DC return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AD2        | + 12               | + 12V Power: + 12V DC system power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AE2        | BDOUT L            | <b>Data Output:</b> BDOUT, when asserted, implies that valid data is available on BDALO-15 L and that an output transfer, with respect to the bus master device, is taking place. BDOUT L is deskewed with respect to data on the bus. The slave device responding to the BDOUT L signal must assert BRPLY L to complete the transfer.                                                                                                                                                                                                                                                                                                                                     |

| AF2        | BRPLY L            | <b>Reply:</b> BRPLY is asserted in response to BDIN L or BDOUT L and during IAK transactions. It is generated by a slave device to indicate that it has input data available on the BDA L bus or that it has accepted output data from the bus.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AH2        | BDIN L             | <ol> <li>Data Input: BDIN is used for two types of bus operations:</li> <li>When asserted during BSYNC L time, BDIN L implies an input transfer<br/>with respect to the current bus master, and requires a response BPPLY L.<br/>BDIN L is asserted when the master device is ready to accept data from a<br/>slave device.</li> </ol>                                                                                                                                                                                                                                                                                                                                     |

|            |                    | <ol><li>When asserted without BDYNC L, it indicates that an interrupt operation<br/>is occurring.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                    | The master device must deskew input data from BRPLY L.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AJ2        | BSYNC L            | Synchronize: BSYNC L is asserted by the bus master device to indicate that it has placed an address on BDALO-15 L. The transfer is in process until BSYNC L is negated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AK2        | BWTBT L            | <ul> <li>Write/Byte: BWTBT L is used in two ways to control a bus cycle:</li> <li>1. It is asserted during the leading edge of BSYNC L to indicate that an output sequence is to follow (DATO or DATOB), rather than an input sequence.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            |                    | <ol> <li>It is asserted during BDOUT L, in a DATOB bus cycle, for byte address-<br/>ing.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AL2        | BIRQ L             | Interrupt Request: A device asserts this signal when its Interrupt Enable<br>and Interrupt Request flip-flops are set. This signal informs the processor<br>that a device has data to input to the processor or it is ready to accept out-<br>put data. If the processor's PS word bit 7 is 0, the processor responds by<br>acknowledging the request by asserting BDIN L and BIAKO L.                                                                                                                                                                                                                                                                                     |

| AM2        | BIAKI L            | Interrupt Acknowledge Input and Interrupt Acknowledge Output: This is an interrupt acknowledge signal which is generated by the processor in response to an interrupt request (BIRQ L). The processor asserts BIAKO L, which is routed to the BIAKI L pin of the first device on the bus. If it is requesting an interrupt, it will inhibit passing BIAKO L. If it is not asserting BIRQ L, the device will pass BIAKI L to the next (lower priority) device via its BIAKO L pin and the lower priority device's BIAKI L pin.                                                                                                                                              |

| AP2        | BBS7 L             | Bank 7 Select: The bus master asserts BBS7 L when an address in the upper 4K bank (address in the 28-32K range) is placed on the bus. BSYNC L is then asserted and BBS7 L remains active for the duration of the addressing portion of the bus cycle.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AR2<br>AS2 | BDMGI L<br>BDMGO L | DMA Grant Input and DMA Grant Output: This is the processor generated daisy chained signal which grants bus mastership to the highest priority DMA device along the bus. The processor generates BDMGO L, which is routed to the BDMGI L pin of the first device on the bus. If it is requesting the bus, it will inhibit passing BDMGO L. If it is not requesting the bus, it will pass the BDMGI L signal to the next lower priority device via its BDMGO L pin. The device asserting BDMR L is the device requesting the bus, and it responds to the BDMGI L signal by negating BDMR, asserting BSACK L, assuming bus mastership, and executing the required bus cycle. |

| AT2        | BINIT L            | <b>Initialize:</b> BINIT is asserted by the processor to initialize or clear all devices connected to the 1/0 bus. The signal is generated in response to a power-up condition (the negated condition of BDCOK H).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

÷

| AU2<br>AV2 | BDALO L<br>BDAL1 L | Data/Address Lines: These two lines are part of the 16-line data/address<br>bus over which address and data information are communicated. Address                                                         |

|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVE        | BUALTE             | information is first placed on the bus by the master device. The same device<br>then either receives input data from, or outputs data to the addressed slave<br>device or memory over the same bus lines. |

| BA2        | +5                 | +5V Power: Normal +5V DC (optional) power for devices requiring this voltage.                                                                                                                             |

| BC2        | GND                | Ground: System signal ground and DC return.                                                                                                                                                               |

| BD2        | + 12               | + 12V Power: + 12V system power                                                                                                                                                                           |

| BE2        | BDAL2 L            |                                                                                                                                                                                                           |

| BF2        | BDAL3 L            |                                                                                                                                                                                                           |

| BH2        | BDAL4 L            |                                                                                                                                                                                                           |

| BJ2        | BDAL5 L            |                                                                                                                                                                                                           |

| BKS        | BDAL6 L            |                                                                                                                                                                                                           |

| BL2        | BDAL7 L            | Data/Address Lines:                                                                                                                                                                                       |

| BM2        | BDAL8 L            | These 14 lines                                                                                                                                                                                            |

| BN2        | BDAL9 L            | are part of the 16-line data/address                                                                                                                                                                      |

| BP2        | BDAL10 L           | bus previously described.                                                                                                                                                                                 |

| BR2        | BDAL11 L           |                                                                                                                                                                                                           |

| BS2        | BDAL12 L           |                                                                                                                                                                                                           |

| BT2        | BDAL13 L           |                                                                                                                                                                                                           |

| BU2        | BDAL14 L           |                                                                                                                                                                                                           |

| BV2        | BDAL15 L           |                                                                                                                                                                                                           |

|            |                    |                                                                                                                                                                                                           |

#### 2.4.3 Bus Cycles --- Figures 2-5, 2-6, 2-7

Overview Every processor instruction requires one or more I/O (input/output) operations. The first operation required is a data input transfer (DATI), which fetches an instruction from the location addressed by the program counter (PC or R7). This operation is called a DATI bus cycle. If additional operations are not referenced in memory or in an I/O device, no additional bus cycles are required for instruction execution. However, if memory or a device is referenced, additional DATI, data input/output (DATIO or DATIOB), or data output transfer (DATO or DATOB) bus cycles are required. Between these bus cycles, the processor can service DMA requests. However, the processor can service interrupt requests only prior to an instruction fetch (DATI bus cycle), and only if the processor's priority is zero (PS word bit 7 is 0).

The following paragraphs describe the types of bus cycles. Note that the sequences for I/O operations between processor and memory or between processor and I/O device are identical. DATO (or DATOB) cycles are equivalent to write operations, and DATI cycles are equivalent to read operations. In addition, DATIO cycles include an input transfer followed by an output transfer. The DATIO cycle provides an efficient means of executing an equivalent read-modify-write operation by making it unnecessary to assert an address a second time.

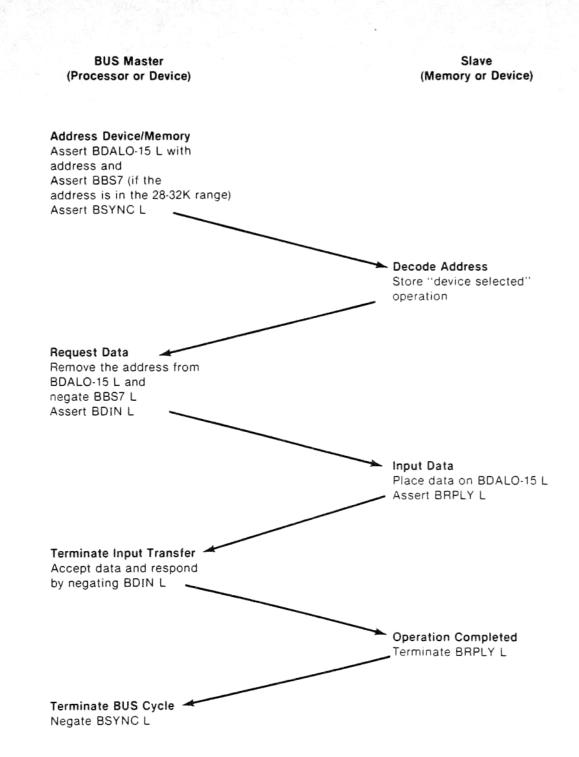

Input Operations — Figures 2-6, 2-7 — The sequence for a DATI operation is shown in Figure 2-5. DATI cycles are asynchronous and require a response from the addressed device or memory. The addressed memory or device responds to its input request (BDIN L) by asserting BRP-LY L. If BRPLY is not asserted within 10 uS (max) after

BDIN L is asserted, the processor terminates the cycle and traps through location 4.

Note that BWTBT L is not asserted during the address time, indicating that an input data transfer is to be executed.

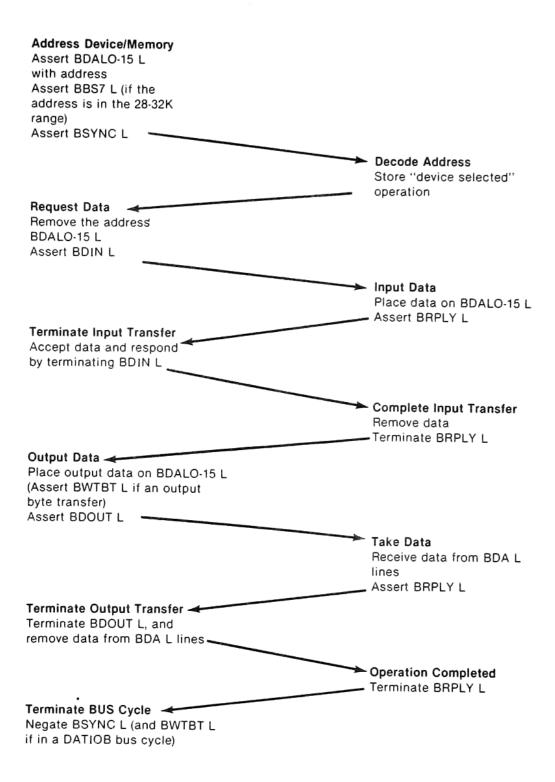

A DATIO cycle is equivalent to a read-modify-write operation. An addressing operation and an input word transfer are first executed in a manner similar to the DATI cycle; however, BSYNC L remains in the active state after completing the input data transfer. This causes the addressed device or memory to remain selected, and an output data transfer follows without any further addressing. After completing the output transfer, the device terminates BSYNC L, completing the DATIO cycle. The actual sequence required for a DATIO cycle is shown in Figure 2-6. Note that the output data transfer portion of the bus cycle can be a byte transfer; hence, this cycle is shown as DATIOB.

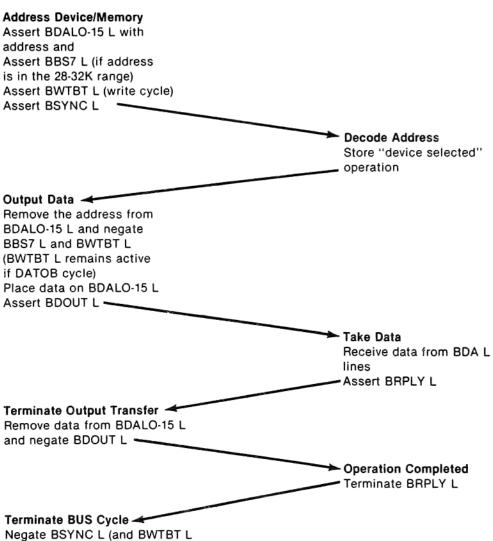

**Output Operations**—Figures 2-6, 2-7—The sequence required for a DATO or the equivalent output byte (DATOB) bus cycle is shown in Figure 2-7. Like the input operations, failure to receive BRPLY L within 10 uS after asserting BDOUT L is an error, and results in a processor time-out trap through location 4.

Note that BWTBT L is asserted during the addressing portion of the cycle to indicate that an output data transfer is to follow. If a DATOB is to be executed, BWTBT L remains active for the duration of the bus cycle; however, if a DATO (word transfer) is to be executed, BWTBT L is negated during the remainder of the cycle.

Bridgeport Machines Division of Textron Inc.

2-7

Figure 2-5 DAT1 Bus Cycle

Bridgeport TEXTRON Bridgeport Machines Division of Textron Inc. BUS Master (Procesor or Device)

Slave (Memory or Device)

Figure 2-6 DATIO or DATIOB Bus Cycle

BUS Master (Processor or Device) Slave (Memory or Device)

if a DATOB bus cycle

Figure 2-7 DATO or DATOB Bus Cycle

Bridgeport, TEXTRON Bridgeport Machines Division of Textron Inc.

#### 2.4.4 Interrupts-Figure 2-8

**Overview** Interrupts are requests made by peripheral devices which cause the processor to suspend temporarily its present program execution and jump to the service routine for the particular interrupt. After completing the service routine, program control is restored to the interrupted program.

An interrupt vector associated with each device is hard wired into the device's interface control logic. This vector is an address pointer that allows automatic entry into the service routine. For example, the front panel keyboard generates an interrupt each time a key is depressed. The vector for the front panel keyboard is 70.

When the processor recognizes the interrupt it stores the condition of the system so that after the interrupt is completed, the program will resume exactly where it left off.

This involves pushing the processor status word (PSW)

and the program counter (PC) onto the system stack.

The effect is: push PSW on stack

push PC on stack

The new contents of the PC and PSW are loaded from two preassigned consecutive memory locations which are called an "interrupt vector". The first word contains the interrupt service routine address (the jump to location), the second word contains the new PSW which will determine the machine status including the operational mode to be used by the interrupt service routine.

After the interrupt service has been completed, a R11 return from interrupt is performed. The two top words on the "stack" are automatically "popped" and placed in the PC and PSW respectively, thus resuming the interrupted program.

| Processor                                                                                                                                                                         | Device                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Strobe Interrupts                                                                                                                                                                 | Assert BIRQ L                                                                                                                 |

|                                                                                                                                                                                   | Receive BDIN L<br>Store "interrupt selected"<br>in device                                                                     |

| Grant Request<br>Pause and assert<br>BIAKO L                                                                                                                                      |                                                                                                                               |

|                                                                                                                                                                                   | Receive BIAKI L<br>Receive BIAKI L and<br>inhibit BIAKO L<br>Place vector on BDALO-15 L<br>Assert BRPLY L<br>Terminate BIRQ L |

| Receive Vector and Terminate<br>Request<br>Input vector address<br>Terminate BDIN L and                                                                                           |                                                                                                                               |

| BIAKO L                                                                                                                                                                           | Complete Vector Transfer Remove vector from BDA L bus                                                                         |